很多人以为 NVMe 才是性能王者,

但真相是:

NVMe 只是“住在 PCIe 这条高速公路上的一种车”。

如果你只看 SSD 参数,却不理解 PCIe,

你看到的永远只是表面性能。

一、什么是 PCIe?它到底“是不是存储协议”?

先把一个90% 人都会混淆的问题说清楚。

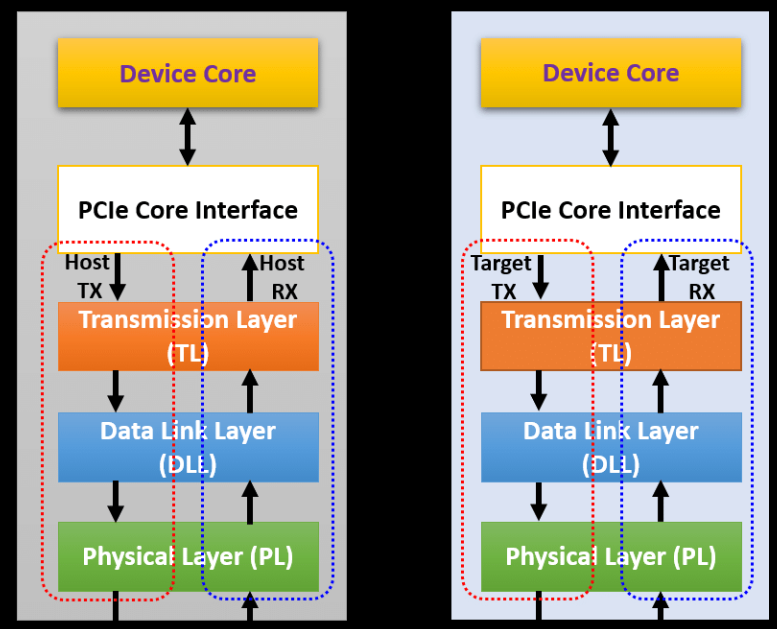

PCIe 的真实身份

PCIe(Peripheral Component Interconnect Express) 本质上是:

一种高速串行互连总线协议

它规定的是:

设备如何与 CPU / 内存通信

数据如何在主板内部高速点对点传输

延迟、带宽、仲裁如何实现

关键结论:

PCIe 不是存储协议,

但它是所有高性能存储协议的“物理与逻辑地基”。

二、为什么要单独讲“PCIe 存储协议”?

因为在存储世界里,出现了一个根本性转变:

旧世界(SATA / SAS 时代)

应用 → 文件系统 → 块层 → SCSI → HBA → 存储协议多

路径长

延迟高

CPU 参与重

新世界(PCIe / NVMe 时代)

应用 → NVMe → PCIe → SSD协议极简

直通 CPU

延迟极低

并发极高

这不是“快一点”,而是“代际差异”。

三、PCIe 的前世:它本来不是为存储而生

1️⃣ 早期使命:替代 PCI / PCI-X

PCIe 的原始目标非常朴素:

替代并行 PCI 总线

解决:

频率瓶颈

共享冲突

带宽不可扩展

于是 PCIe 做了三件关键的事:

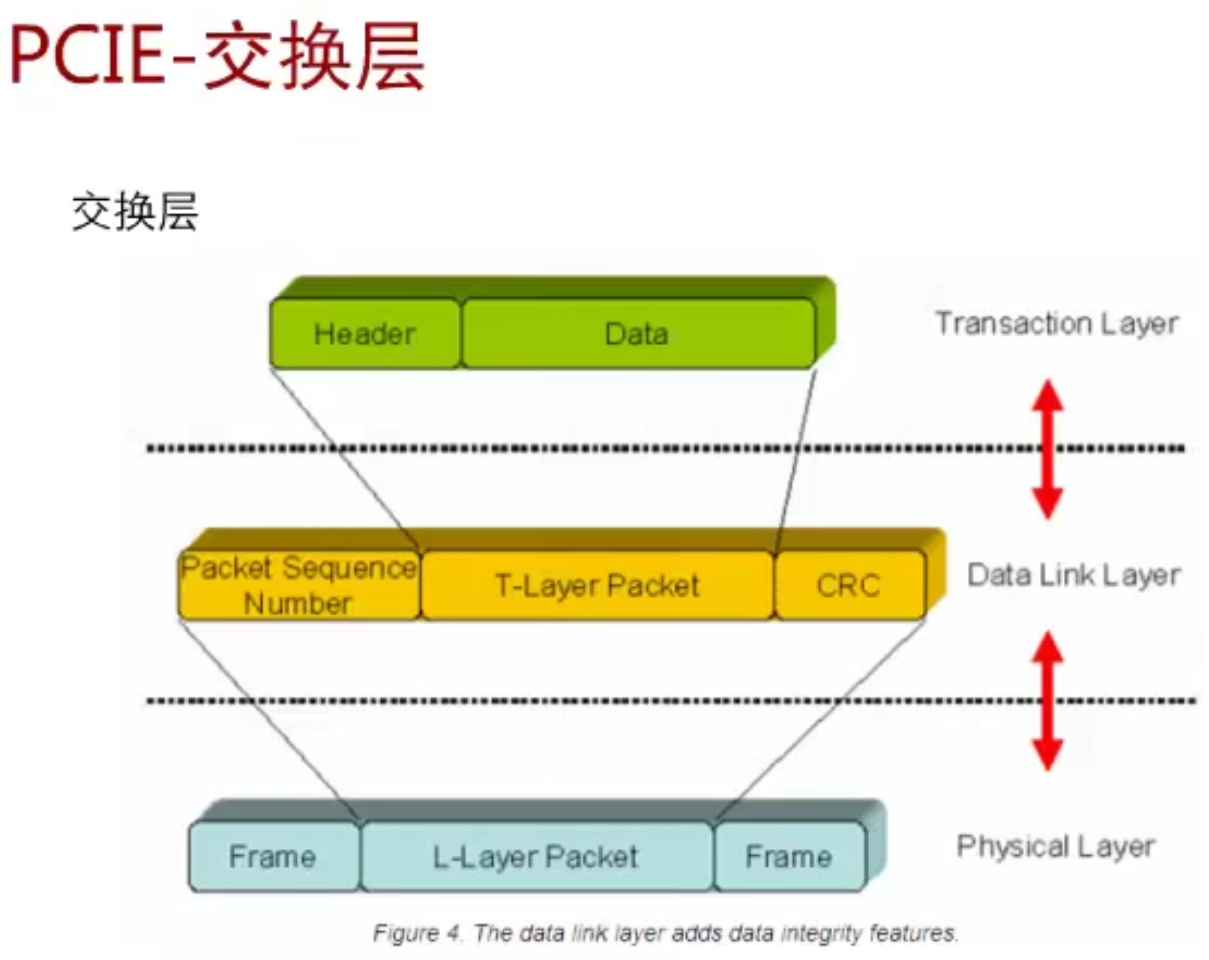

并行 → 串行

共享 → 点对点

总线 → 交换结构

这为后来“存储直连 CPU”埋下了伏笔。

2️⃣ 为什么 PCIe 天生适合存储?

因为存储最需要的三样东西,PCIe 都“刚好擅长”:

四、PCIe 的核心机制:为什么它这么快?

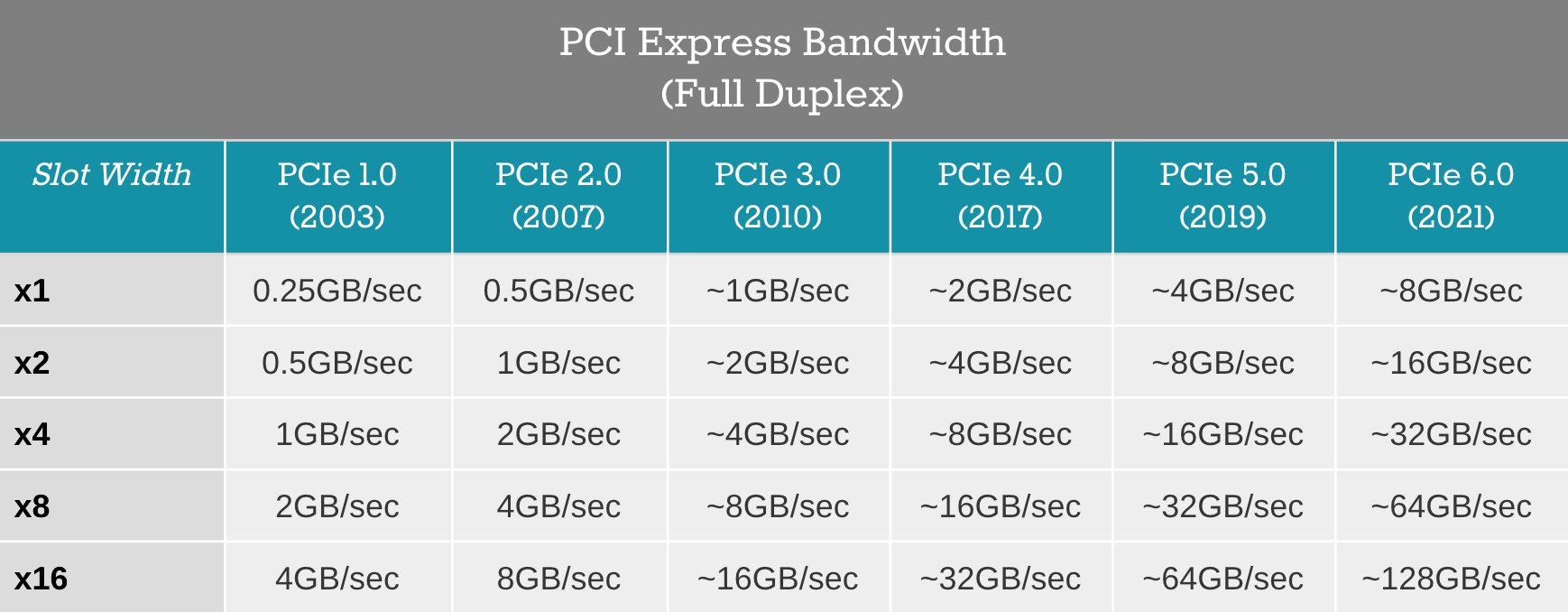

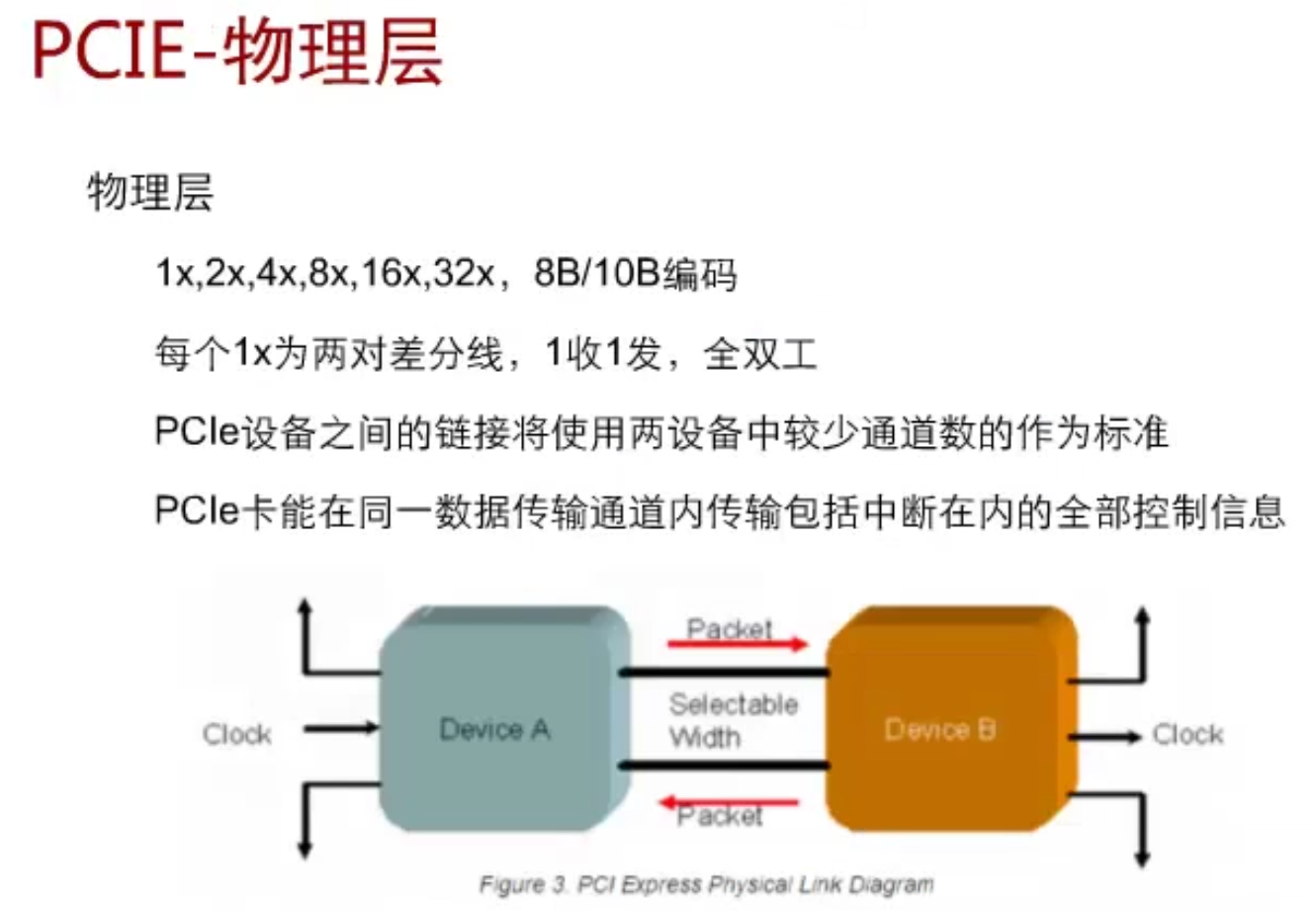

1️⃣ Lane(通道)机制

PCIe 不讲“总带宽”,而讲 Lane:

x1 / x2 / x4 / x8 / x16

每条 Lane 都是 全双工

举例(PCIe 4.0):

x4 ≈ 8 GB/s

x16 ≈ 32 GB/s

这正是 NVMe SSD 用 x4 就能打爆 SATA 的原因。

2️⃣ 点对点 + 交换架构

每个设备都有“独立通道”

不再争抢总线

延迟稳定、可预测

这对数据库、虚拟化、AI 至关重要。

3️⃣ DMA 与中断优化

PCIe 允许设备:

直接 DMA 访问内存

极少 CPU 参与

批量提交请求

存储从“CPU 主导”变成“设备自治”。

五、PCIe 与传统存储协议的本质差异

PCIe vs SATA / SAS

NVMe 的成功,根源在 PCIe,而不是 NVMe 本身。

六、PCIe 在存储体系中的三种角色

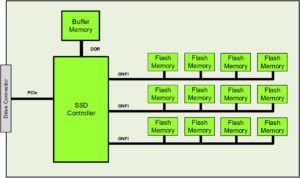

① 本地直连存储(最常见)

NVMe SSD

直插主板 / U.2 / M.2

延迟最低、性能最好

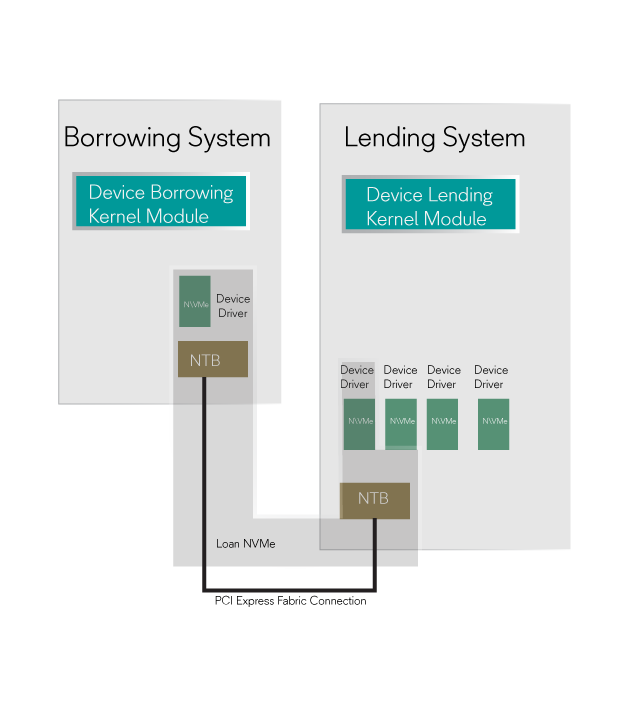

② 设备级存储池(PCIe Switch)

多块 NVMe

通过 PCIe Switch 共享

高端服务器、存储阵列

③ 远程化的“伪直连”(趋势)

PCIe over Cable

PCIe Fabric

CXL(下一代)

让 PCIe 突破“只能在一台机器里”的限制

七、为什么说:NVMe ≠ PCIe?

这是一个极其重要的认知点。

PCIe:高速公路

NVMe:为 SSD 设计的交通规则

如果你用错了比喻:

NVMe 再先进

跑在低代 PCIe / 少 Lane 上

一样会“堵车”

性能瓶颈 80% 出在 PCIe 拓扑,而不是盘。

八、PCIe 的现实瓶颈与误区

❌ 误区 1:只看 PCIe 代际

PCIe 5.0 x2

可能不如 PCIe 4.0 x4

❌ 误区 2:忽略 CPU 直连与否

直连 CPU

还是走 PCH / 南桥

性能差距巨大

❌ 误区 3:忽略 NUMA 与拓扑

跨 CPU Socket

跨 Root Complex

延迟成倍上升

高端存储调优,本质是 PCIe 拓扑调优。

九、PCIe 的“今生”:正在吞噬整个存储世界

今天,PCIe 已经在做三件“以前不属于它的事”:

吞噬磁盘协议(NVMe)

侵入网络领域(NVMe-oF 的根)

挑战内存边界(CXL)

存储、内存、网络,正在 PCIe 上“融合”。

十、未来:PCIe + CXL,会改变什么?

当:

存储可以像内存一样访问

内存可以池化

设备可以跨主机共享

传统“本地存储 / 网络存储”的边界将被彻底打破。

十一、总结一句话

PCIe 并不是一个“存储协议”,

但它决定了:

——现代存储,究竟能快到什么程度。

理解 PCIe,

你才真正理解了:

NVMe 为什么快

存储为什么“突然跃迁”

未来数据中心为什么会重新洗牌